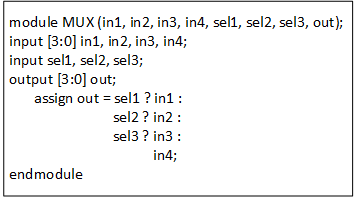

I have used a signal instead of an variable here, because variables are harder to debug.

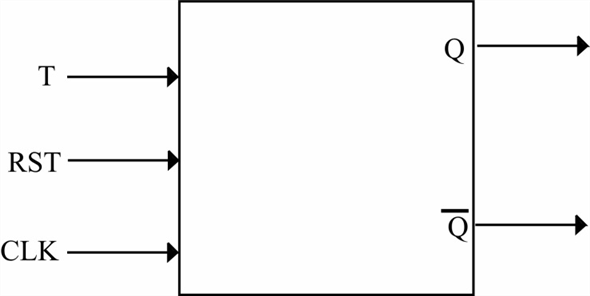

The state of the SR flip-flop is saved in the signal Q. If rising_edge(clock) then - flip-flop triggered at the rising clock edge The code style is as follows: signal Q : std_logic - declare signal in the declarations part of the architecture You can describe a clock-edge triggered SR flip-flop in VHDL which is then mapped to the D flip-flop of the FPGA by the synthesis tool. So, the designer has not to worry about glitches! The timing analyzer of the FPGA toolchain ensures, that the evaluation of the above expression is completed before the next rising (or falling) clock-edge. To circumvent this problem, the FPGA offers D flip-flops which state is only updated on clock-edges. To notify the designer, that latches are susceptible for glitches, the synthesis compiler issues the above warning. If one of these gates is switching faster than another one, there might be an intermediate result, where the expression is true and, thus, your latch becomes '1'. Instead the multi-bit comparator for the <= operator may produce a glitch because the comparator itself is composed of several gates. But, this cannot be ensured in real hardware because the expression is not evaluated at once. According to the above expression, the latch should keep in state '0'. Now let the temperature fall to Tact = Tset-1. This works as long as Tact is not changing. Now image a point in time, when the latch is currently in state '0' and Tact = Tset. Your latch is set when the expression Tact <= (Tset - 2) is true.

This works fine in simulation but makes problems in FPGAs as well as digital circuits build from discrete components. You have described a SR latch for the signal ONOFF.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed